Ein Beitrag zur Analyse des Schaltverhaltens unipolarer SiCTransistoren

In dieser Arbeit wird das Schaltverhalten von SiC-JFETs analysiert, wobei ein Schwerpunkt auf Reverse Recovery Verhalten der Bodydiode liegt.

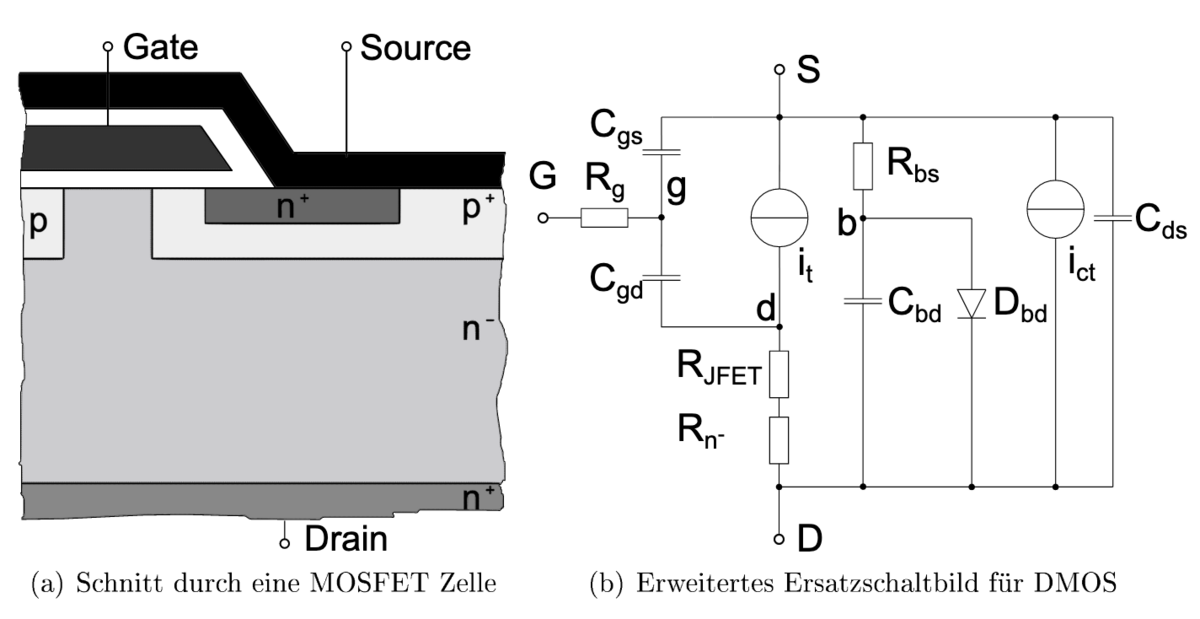

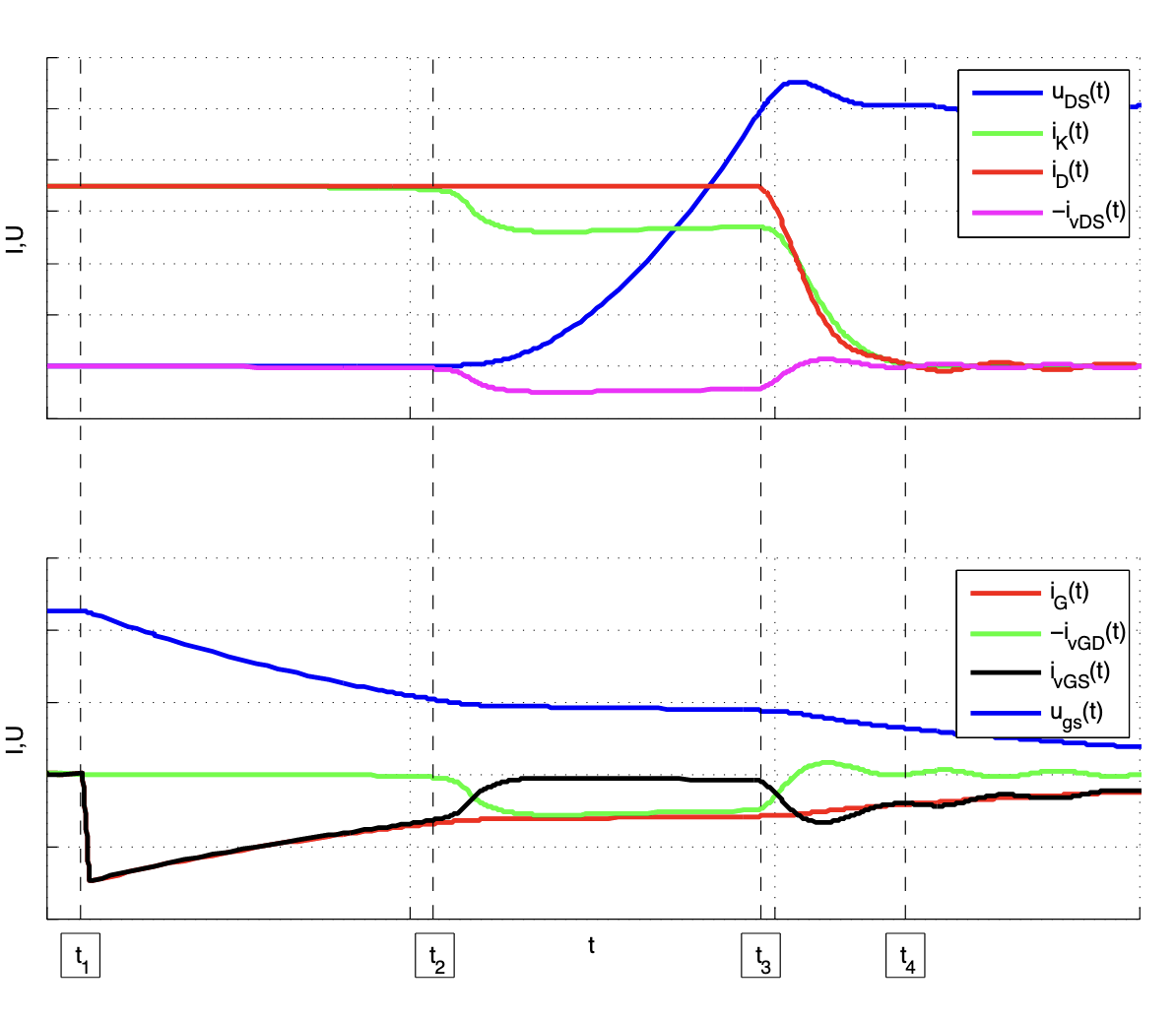

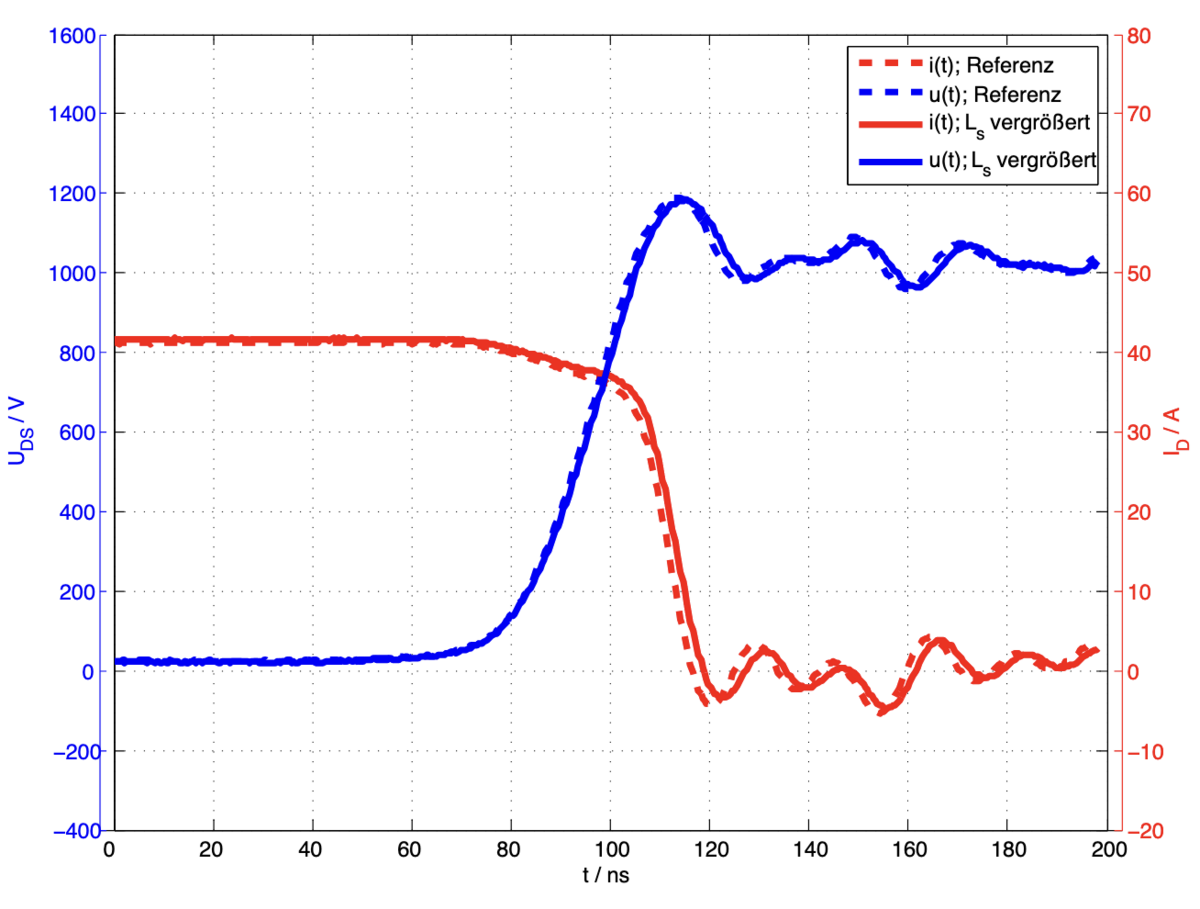

Das Reverse Recovery der Body-Diode eines unipolaren Transistors beim Schalten induktiver Lasten zeigt eine typische Ladung. Sie kann durch Analyse verschiedener Experimente mit dem Halbleiter in drei Arten unterteilt werden. SiC-Halbleiter weisen im Vergleich zu Si-Halbleitern eine um eine Größenordnung höhere Sperrschichtkapazität auf, da die Feldstärken im Halbleiter in gleichem Maße größer sind. Hierdurch wird beim Reverse Recovery eine bemerkenswerte Menge an Ladung messbar. Anhand von Messungen und Vergleichen ist dies deutlich zu erkennen. Dies wirkt sich auf das Schaltverhalten des Transistors und die Verlustaufteilung aus, was in ergänzenden Simulationen gezeigt wird. Die beim Reverse Recovery entstehenden Verluste sind durch eine äquivalente Ladung beim Forward Recovery kompensiert. Aus diesem Grund zeigt die Schottky-Diode beim Schalten keine Verlustleistung. Durch Benutzung der Body-Diode baut sich im Halbleiter ein Plasma auf. Dies verhindert das Synchrongleichrichten in Abhängigkeit der Verriegelungszeit. Schon nach sehr kleinen Verriegelungszeiten wird durch die Extraktion des Plasmas während des Reverse Recovery eine Ladung messbar. Diese Ladung ist vom Laststrom und der Temperatur der Sperrschicht abhängig. Eine erhöhte Reverse Recovery Ladung tritt beim schnellen Schalten auf, hierfür können Defektelektronen in der Raumladungszone verantwortlich sein. Die aktuellen SiC-Transistoren neigen beim Reverse Recovery zum parasitären Aufsteuern, wodurch eine weitere Ladung verursacht wird. Dem parasitären Aufsteuern können Designvorschläge entgegenwirken. Hierzu wird die vorhandene und als störend angesehene parasitäre Induktivität am Source genutzt. Es entsteht eine Rückkopplung, die das parasitäre Aufsteuern verhindert. Sie beeinflusst das Einschalten des Halbleiters negativ und muss durch eine konstruktive Lösung umgangen werden. Die parasitären Gatewiderstände der aktuellen SiC-Halbleiter und die parasitären Induktivitäten kann eine erhöhte Einschalt- und Ausschaltspannung ausgleichen.